ecosnos.ru

|

ecosnos.ru |

|

|

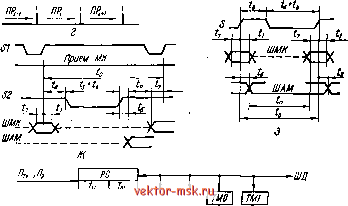

Главная Микроустройства: номенклатура изделий электронной промышленности 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 [ 24 ] 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 Операция Операнд Код операции Пояснения Счет со сдвигом UAC(B + q) ЛАС(В + <?) ПЦС (В + <?) ПЦС (B + q) ЛЦС (В + q) ЛПС (B + q) ПЛС (В + q) ЛЛС (B + q) Счет с двойным сдвигом: ПДАС (В + (?) ЛДАС (В + (?) ПДЦС (В + (?) ПДЦС (В + (?) ЛДЦС (В + q) ЛДЦС (В + q) ПДЛС (В + (?) ЛДЛС (В + д) о о о о о о о о о о о о о о о о РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР РР 0000 0010 0001 1001 ООП 1011 1000 1010 0100 оно 0101 1101 0111 1111 1100 1110 101 101 101 101 101 101 101 101 к младшему разряду содержимого РР прибавляется перенос q. Результат со сдвигом на один разряд фиксируется на PP. При этом сдвиг осуществляется по правилу левого арифметического (ЛАС), циклического (ЛЦС) или логического (ЛЛС) сдвигов или правого арифметического (ПАС), циклического (ПЦС) или логического (ПЛС) сдвигов. Передача информации при указанных сдвигах показана на рис. 2.4, и 101 101 101 101 101 101 101 101 к младшему разряду содержимого РР прибавляется перенос q. Результат со сдвигом на один разряд фиксируется на PP. При этом сдвиг осуществляется по правилу правого двойного арифметического (рис.2.4, s) циклического (рис. 2.4 к) или логического (рис. 2.4, и) сдвигов или левого двойного арифметического (рис. 2.5, а), циклического (рис. 2.4, ж) или логического (рис. 2-5, а) сдвигов. При этом двойные арифметические сдвиги Б зависимости от сигнала .на входе Я О выполняются с одним (ПО = 1) или двумя (ПО =0) знаковыми разрядами. Во втором случае сдвиг осуществляется по схеме, показанной на рис. 2.5, б и е. На всех с?семах верхний регистр является РР, а нижний - РД поМКЯПООО) результат на регистрах не фиксируется, а выдается на ШД по мере его формирования.- Независимо от работы АЛУ и мультиплексоров функционирует счетчнк команд СК, в качестве которого используется Р0Н7. По каждому нарастающему перепаду СС (рис. 2.5, г) СК получает приращение, величина которого зависит от позиции ИМС и сигналов на входах 22 и 27 (табл. 2.34). В промежуточной или старшей позиции приращение определяется только сигналом на входе 22 (выход 27 в этом случае является выходом старшего разряда шины Л). При использовании СК в качестве РОН (например, при засыл-

в   /7 ...,/7.

Рис. 2.5. 2.34. Приращение в ИМС ВИ1

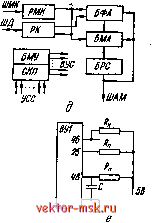

кода СК ке в СК кода) для правильной работы ИМС на его инверсный счетный вход (вывод 22) следует подавать едилицу, так как в противном случае может произойти сбой из-за одновременного выполнения несовместимых МО приема и приращения кода. Сложные арифметические операции (умножение, деление и др.))еализуются в МП программным путем. В табл. 2,35 приведен микроалгоритм умножения с младших разрядов множителя и сдвигом суммы частичных произведений двух 42разрядных чисел на одной ИМС, на которую подаются сигналы П1=П0=1, а в табл. 2.36 представлена цифровая диаграмма состояний основных узлов ИМС при умножении чисел И и 13 по указанному микроалгоритму. В качестве единицы времени при построении цифровой диаграммы взят такт, равный одному периоду СС, отсчитанному от начала высокого уровня, возникшего после переключающего перепада. Вследствие этого в такте О на ИМС подается MKD, код которой в течение такта О преобразуется КС и поступает на входы РО. Завершается такт О подачей на ИМС переключающего (нарастающего) перепада, по которому преобразованный код МК фиксируется на РО. В первом н последующих тактах вводится и принимается на РО очередная МК и выполняется введенная в предыдущем такте МК. Аналогичным образом можно составить программу деления двоичных чисел. Для правильного функционирования МП, состоящего из нескольких ИМС, их выводы должны быть соотйетствующим образом соединены. На рис. 2.4, е показано соединение выводов 6, 9, It и 12, обеспечивающих передачу информации при сдвигах. В зависимости от реализуемого сдвига (табл. 2.37) к указанным выводам подключаются выходы Вых. или входы Вх. младших PPq, РДо или старших РРз, РДз разрядов регистров РР или РД, либо константа 0. При реализации некоторых с')1вигов отдельные выводы не используются (например, вывод 12 при правом арифметическом сдвиге). Так как передача информации между ИМС осуществляется в инверсном коде, то на выводах 6, 9, И и 12 можно наблюдать инверсные значения сигналов, указанных в табл. 2.37. Например, на выводе 6 при левом двойном логическом (ЛДЛ) сдвиге будет сигнал 1, а при левом циклическом (ЛЦС) сдвиге - инверсное значение цифры, хранящейся в PPg. Быстродействие ИМС определяется задержками в распространении сигналов, значения которых приведены в табл. 2.38. 2.5. МИКРОПРОГРАММНОЕ УПРАВЛЕНИЕ В МИКРОСХЕМАХ СЕРИИ 584 Блок микропрограммного управления ВУ1 (рис. 2.5, д) осуществляет формирование адресов, по которым из ПЗУ микропрограмм извлекаются МК. Он состоит из 16- и 14-разрядиых регистров команд РК и микрокоманд РМК, блоков местного управления БМУ, формирования и модификации адресов МК БФА п БМА и регистров стека БРС. В свою очередь, БРС состоит из двух 10-разрядных |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||