ecosnos.ru

|

ecosnos.ru |

|

|

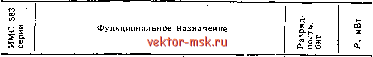

Главная Микроустройства: номенклатура изделий электронной промышленности 1 2 3 4 5 6 7 8 9 10 11 12 13 [ 14 ] 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 Команда умножения в МП отсутствует. Вследствие этого умножение производится программным путем. В табл. 1.18 приведен пример умножения двух положительных 16-разрядных двоичных чисел, записанных в регистрах РВС и PDE. Умножение начинается со старших разрядов множителя и со сдвигом суммы частичных произведений в два этапа. На 1-м этапе умножают на младший байт множителя, а па 2-м - на старший. После этого два полученных произведения суммируются с учетом взаимного сдвига на один байт. При том старший байт произведения, полученного на 1-м этапе, суммируется за счет предварительной его заеылки в PL: Три старших байта результата расположены в регистрах РА и PH.L, младший байт - в ЗУ по адресу а. Деление так же как и умножение выполняется в МП программно. В табл. 1.19 приведена программа деления с восстановлением остатка двухбайтных положительных чисел. При этом предполагается, что делитель больше делимого, делимое в старшем разрядесодержит О и находится в ячейках ЗУ с адресами а и а -f 1 (старший байт хранится по адресу а + 1), а делитель расположен в регистре PDE. Частное формируется в РВС, а конец деления определяется с помощью маркерной 1, которая после определения 16 бит частного перейдет в TQ. Глава 2 МИКРОПРОЦЕССОРНЫЕ НАБОРЫ СЕРИЙ 583 и 584 2.1. ЦЕНТРАЛЬНЫЙ ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ ВС1 СЕРИИ 583 Схемно-технологической основой ИМС серий 583 и 584 является ИИЛ. Серия 583 [J9, 38] выпускается в виде двух модификаций (583 и К583), состав и основные параметры которых-приведены в табл. 1.2 и 2.1. При разработке микроп[50цессорных систем на осг нове ИМС этой серии необходимо учитывать то, что серия функционирует в отрицательной логике (1 соответствует низкий потенциал). Центральный процессорный элемент ВС1 состоит (рис. 2.1, а) нз арифметического устройства АУ, запоминающего устройства ЗУ в виде 16 регистров общего назначения РОН, блока управления БУ, вырабатывающего внутренние управляющие сигналы ВУС, и вспомогательных регистров результата РР, управления РУ, состояния PC, микрокоманды РМ и двух буферных регистров РБ1 и РБ2. Регистры РМ и' PC состоят соответственно из 16 и 2 разрядов, а остальные - из восьми. Следует отметить, что кроме указанных регистров других запоминающих элементов ни в Б У, ни в АУ нет. Остальную часть ИМС составляют исключительно КС. Назначение выводов ИМС приведено в табл. 2.2. Обмен информацией осуществляется по двум двунаправленным шннам данных ШД1 и ШД2, шине микрокоманд ШМ и шине управления ШУ, включающей в себя одно- и двунаправленные выводы и служащей для ввода или вывода управляющих сигналов, а также для каскадирования И.МС при увеличении разрядности, кратной 8 (табл. 2.2). Мик.росхема работает с числами, представленными в дополпительно'м коде. Для указания знака отводится один (старший) разряд, который отделяется от мантиссы числа фиксированной запятой. Выделяется знаковый разряд сигналом К на входе 2.1. Основные параметры ИМС серии 583  ВА1 ВА2 ВАЗ ВА4 ВГ1 ВГ2 ВМ1 BCI ВС2 вез ВС4 ВУ1 РА1 ХЛ1 Приемопередатчик магистральный с памятью без памяти Универсальный коммутатор / Коммутатор магистралей Контроллер-синхронизатор Контроллер предварительной обработки ин формации Микропроцессор логический Центральный процессорный элемент Умножитель Арифметический микропроцессор Универсальный Масочная программируемая логическая матрица Генератор адресов микрокоманд Коммутационный микропроцессор Ассоциативное запоминающее устройство Ко.миутатор магистральный 20X18 16X8 . 500 500 250 400 260 360 340 290 360 340 250 ЗУ. При = 1 все разряды чисел в данной ИМС обрабатываются как разряды мантиссы. При К = О старший разряд обрабатывается как знаковый, а все остальные - как разряды мантисс. Отличия в обработке знакового разряда и разрядов мантисс проявляются при переполнении разрядной сетки и при сдвигах. Под переполнением понимается выход результата за пределы диапазона (-1, 1). Это возможно при сложении на сумматоре чисел одного знака, сумма которых по модулю больше. 1. Переполнение разрядной сетки сопровождается появлением сигнала' = I (вых'од 29), который формируется по правилу 9 = V qoi) V Kqo, где - перенос из знакового разряда; , - перенос из старшего разряда мантиссы в знаковый разряд. Такое правило формирования сигнала q объясняется тем, что при переполнении разрядной сетки перенос в знаковый разряд сопровождается отсутствием переноса из знакового разряда или отсутствие переноса в знаковый разряд сопровождается переносом из знакового разряда. Так как переполнение связано с ошибочным изменением знака, то ИМС восстанавливает его. Если же переполнения разрядной сетки нет, то q = q. При К = 1 переносы % п 9, не анализируются, так как на месте знакового разряда находится старший разряд из данной группы разрядов мантиссы и его обработка осуществляется так же, как и остальных разрядов мантиссы. Примеры действий с числами в старшей (/С = 0) и младшей (К ~ 1) ИМС приведены в табл. 2.3. Другое отличие в обработке знакового разряда и разрядов мантиссы проявляется при сдвигах, особенности реализации которых поясняет рис. 2.1, б. При левом арифметическом сдвиге ЛАС в старшей ИМС {К = 0) знаковый разряд (отмечен цифрой Oi отключается от остальных разрядов и в сдвиге не участвует. Bet разрядм мантиссы перемещаются на одну позицию влево, в младший разряд младшей ИМС (К - 1) записывается О, а старший разряд манти, сы (отмечен цифрой I) старшей ИМС (К = 0), выходящий за пределы разрядной сетки после завершения сдвига (выдвигаемый раз- г-\РУ \ ЁУС PC -J ллс 0..J РОН -лт \D...7 шдг ПАС ц'е \/...7[0...7\-S- □ -с пцс А L а

tS..2} \2U1

А А ШМ ШХ ВМ1 2 3 - ШУ-- А RMI 5 Z L А К'О 1 £J- д Рис. 2.1. ряд), выдается на выход А. При правом арифметическом сдвиге ПАС (цифра в знаковом разряде не изменяется) все разряды мантиссы перемещаются на одну позицию вправо, в старший разряд мантиссы записывается цифра из знакового разряда, а на выход А выдается цифра из младшего (выдвигаемого разряда). Принципы реализации левых и правых логических (ЛЛС, ПЛС) и циклических (ЛЦС, ПЦС) сдвигов также поясняет рис. 2.1, б. Для формирования признака А и выполнения указанных сдвигов входы и выходы ИМС должны быть соответствующим образом соединены? |